SoundTraxx Mobile Decoders

# MC1 Series Technical Reference

Software Release 1.00

#### Notice

The information in this document is subject to change without notice.

SoundTraxx (Throttle Up!) shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or consequential damages resulting from the furnishing, performance or use of this material.

This document contains information protected by copyright. No part of this document may be photocopied or reproduced in any form without the prior written consent of Throttle Up! Corp.

Product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

SoundTraxx is a registered trademark of Throttle Up! Corp. SoundTraxx DCC, and Hyperlight are trademarks of Throttle Up! Corp.

## CV 1 Primary Address Control

### Description

Contains the decoder's primary address between 1 and 127:

| Bit 7            |    |    |                         |    |    |          | Bit 0    |

|------------------|----|----|-------------------------|----|----|----------|----------|

| 0                | A6 | A5 | A4                      | A3 | A2 | A1       | A0       |

| Bit 0-<br>Bit 7: | -  |    | Decoder A<br>I. Must be |    |    | <u>.</u> | <u>.</u> |

The decoder will process all valid instruction packets containing an address that matches the value contained in this register when CV 29, bit 5 is set to 0.

Programming this register with a new value will automatically clear the Consist Address (CV 19) to 0 and clear the Extended Address Enable bit in CV 29 (bit 5).

The decoder will ignore commands that attempt to program this register with values outside the range of 1 to 127.

Note that CV 1 can only be changed in operations mode if the extended address is enabled.

Default Value:3Related CVs:See also CV 29, Consist Address, Extended Address

## CV 2 Vstart

### Description

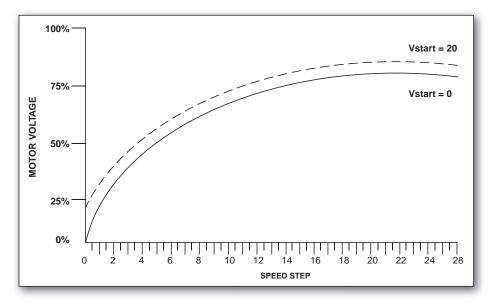

Vstart defines the initial voltage level applied to the motor at speed step 1 as a fraction of available supply voltage:

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

D0-D7: Motor Start Voltage

Vstart may contain any value from 0 to 255. The starting voltage applied to the motor may be computed as:

#### Starting Voltage = Supply Voltage X CV2÷255

where CV 2 is the contents of the Vstart register. A value of 0 corresponds to a zero starting voltage. A value of 255 corresponds to the maximum available voltage (100%).

For speed steps greater than 1, the decoder will continue to sum the initial starting voltage level into the throttle computations which has the effect of offsetting all points on a given speed curve by the level set by Vstart as illustrated in the figure below.

Default value: 0

## CV 3 Baseline Acceleration Rate

### Description

Contains a value between 0 and 255 that sets the decoder's acceleration rate:

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

D0-D7: Baseline Acceleration Rate

Acceleration rate may be computed as:

#### seconds/speed step = CV 3 x 0.896+Number of speed steps

When this CV is set to 0, the locomotive speed will respond nearly instantly to increases in the throttle setting, equivalent to no momentum. When set to 255, it will take approximately 3.8 minutes to accelerate to full speed from a standing stop.

It is recommended that this CV be set to a nonzero value when operating the decoder in 14 or 28 speed step modes as the throttle will interpolate between speed steps during acceleration to produce a smoother overall response.

| Default value: | 0                                                    |

|----------------|------------------------------------------------------|

| Related CVs:   | See also Baseline Braking Rate, Consist Acceleration |

|                | Rate, Consist Brake Rate.                            |

## CV 4 Baseline Braking Rate

### Description

Contains a value between 0 and 255 that sets the decoder's braking rate:

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

**D0-D7:** Baseline Braking Rate

Braking rate may be computed as:

#### seconds/speed step = CV 3 x 0.896+Number of speed steps

When this CV is set to 0, the locomotive speed will respond nearly instantly to decreases in the throttle setting. When set to 255, it will take approximately 3.8 minutes to brake to a stop from full speed.

It is recommended that this CV be set to a nonzero value when operating the decoder in 14 or 28 speed step modes as the throttle will interpolate between speed steps during braking to produce a smoother overall response.

Default value: Related CVs:

0

See also Baseline Acceleration, Consist Acceleration Rate, Consist Brake Rate.

## CV 7 Manufacturer Version ID (Read Only)

### Description

Contains 8-bit software version identifier.

| Bit 7 |            |        |    |    |    |    | Bit 0 |

|-------|------------|--------|----|----|----|----|-------|

| D7    | D6         | D5     | D4 | D3 | D2 | D1 | D0    |

| D0-D  | 7: Versior | n Code |    |    |    | -  |       |

-----

80 = Mobile Decoder, V1.0

This CV is read only and cannot be modified.

## **CV 8 Manufacturer ID**

### **Description**

Contains the NMRA issued Manufacturer ID code assignment for SoundTraxx/Throttle Up! (141):

#### Bit 7

| Bit 7 |   |   |   |   |   |   | Bit 0 |

|-------|---|---|---|---|---|---|-------|

| 1     | 0 | 0 | 0 | 1 | 1 | 0 | 1     |

Writing a value of 8 to this CV will reset all CVs to their default value. All other write operations will be ignored.

## CV 10 BEMF Cutout

### Description

This is used to gradually reduce the effect of the BEMF Control as locomotive speed is increased. This CV contains a value from 0-127 that corresponds to the speed step at which the intensity of BEMF control will be reduced to zero.

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

**D0-D7:** BEMF Cutout

This CV can alternatively contain a value from 128-255 which will cause the BEMF intensity to decrease to a percentage between 0 and 50% of the BEMF intensity set by CV 212 as:

Full Speed BEMF Intensity = (CV 212 - 128)÷128

Default value: 0

## CV 11 Packet Time Out Value

### Description

Contains a value between 0 and 255 corresponding to the time period that is allowed to elapse between receipts of a valid packet addressed to the decoder before a throttle shutdown occurs.

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

D0-D7: Packet Time-out Value

The time out period is computed in seconds as:

#### Time Out Period = CV 11 X 0.25

A CV value of 0 disables the time out period and the locomotive will run indefinitely without receiving another packet.

For all other values, the decoder maintains an internal timer, which is reset every time the decoder receives a valid broadcast address packet or other valid packet whose address matches its primary address or, if enabled, the extended address or consist address.

In the event no valid packets are received within the prescribed time period, the decoder will bring the locomotive to a stop at the rate set by CV 4 or CV 24. The state of the auxiliary function outputs will remain unchanged.

## CV 15 CV Unlock Register

### Description

Contains a value from 0-7 that is used to unlock access to the decoder's CVs in a multi-decoder installation.

CV 15 may always be written or verified regardless of the decoder's lock status. An acknowledgment will only be generated, however, when the decoder is unlocked.

| Bit 7 |   |   |   |   |    |    | Bit 0 |  |

|-------|---|---|---|---|----|----|-------|--|

| 0     | 0 | 0 | 0 | 0 | D2 | D1 | D0    |  |

D0-D2: Unlock Code

Locked State If CV 15 does not match CV 16, all read and write operations to the decoder will be ignored and no acknowledgment is generated.

Unlocked State Access to the decoder's CVs occurs only when CV 15 = CV 16.

*Note:* CVLCKE Bit in CV 30 must be set to enable the lock feature in CVs 15 and 16.

## CV 16 CV Lock ID Code

### **Description**

Contains a value from 0-7 that sets the unlock code that must be programmed into CV 15 in order to access the decoder's CVs in a multi-decoder installation.

CV 15 may always be written or verified regardless of the decoder's lock status. An acknowledgment will only be generated, however, when the decoder is unlocked.

Bit 7

| 0 0 0 | 0 0 | ID2 ID1 | ID0 |

|-------|-----|---------|-----|

|-------|-----|---------|-----|

ID0-ID2: CV Lock Code

*Note:* CVLCKE Bit in CV 30 must be set to enable the lock feature in CVs 15 and 16.

Default Value:0Related CVs:See also Error Information/Alternate Mode Selection.

## CV 17,18 Extended Address

### Description

CV 17 and 18 make up a 'paired' CV, meaning that the two CV registers taken together hold one piece of data; in this case, the 14-bit extended decoder address:

#### **CV 17 Extended Address MSB**

| Bit 7 |     |     |     |     |     |    | Bit 0 |

|-------|-----|-----|-----|-----|-----|----|-------|

| A15   | A14 | A13 | A12 | A11 | A10 | A9 | A8    |

#### CV 18 Extended Address LSB

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| A7    | A6 | A5 | A4 | A3 | A2 | A1 | A0    |

The extended address allows the decoder to be assigned one of 10,179 addresses ranging from 0xC000 to 0xE7FF (Note however, that most command stations will only recognize addresses 0000 through 9999.). The extended address will only be recognized by the decoder when CV 29, bit 5 is set to 1. Once this bit is set, the decoder will no longer recognize its primary address until CV 29, bit 5 is cleared.

CV 17 contains the most significant byte and must be loaded with values within the range of 0xC0 and 0xE7. CV 18 contains the least significant byte and may contain any value.

To determine the extended address value, add the desired four-digit address to the number 49152. Divide this number by 256 and record the quotient and the remainder. CV 17 is then programmed with the quotient value and CV 18 is programmed with the remainder value.

Example: Compute CV 17 and 18 register values for extended address 7152.

| 1. Add 7152 to 49152:   | Sum = 56304.   |                 |

|-------------------------|----------------|-----------------|

| 2. Divide 56304 by 256: | Quotient = 219 | Remainder = 240 |

| 3. Program CV 17 to 219 |                |                 |

| 4. Program CV 18 to 240 |                |                 |

Note: Most command stations will handle these computations automatically

when setting the extended address. However, it's still nice to know how to derive them.

Because CV 17 and 18 make up a paired CV, programming order is important. CV 17 must be written to first, followed by a write to CV 18. The decoder will ignore commands that attempt to program these registers out of order or with values outside the allowed range of 0xC000 to 0xE7FF.

These CVs may be changed in service mode at any time, but in operations mode only when CV 29, bit 5 is cleared (i.e., CV 1, Primary Address is enabled).

Default Value:CV 17 = 192, CV 18 = 03 (Long Address 0003)Related CVs:See also Primary Address, CV 29, Consist Address.

## CV 19 Consist Address

### Description

Contains address and direction data for consist operation:

| Bit 7            |    |         |                                                     |                         |    |    | Bit 0 |

|------------------|----|---------|-----------------------------------------------------|-------------------------|----|----|-------|

| CDIR             | A6 | A5      | A4                                                  | A3                      | A2 | A1 | A0    |

| Bit 0-<br>Bit 7: | -  | CDIR, C | Consist Ad<br>Consist Dir<br>0 = Norma<br>1 = Rever | rection<br>al Direction | n  |    |       |

The CDIR bit defines orientation of the locomotive within a consist and specifies whether the direction bit in a speed/direction data packet should be inverted.

Bits A0-A6 assigns the consist address from 0 to 127. If A0-A6 = 00, consist commands are ignored. Otherwise, if the decoder receives a valid command packet whose address matches the consist address, the packet will be processed as any other packet with the following exceptions:

Long Form CV Access instructions will be ignored.

The direction bit in a speed/direction or advanced operation packet is inverted if CDIR = 1.

Only the auxiliary functions enabled in CV 21 and CV 22 are allowed to change.

When the consist address is active, speed/direction and advanced operations packets sent to the decoder's primary address (or extended address, if enabled) will be ignored. All other instruction packets sent to the decoder's primary (or extended) address, including CV access and function control, will continue to be processed as normal.

In summary, setting CV 19 to 0 or 128 disables consist addressing. Setting CV to a value between 1 and 127 enables consist addresses 1 to 127 with the locomotive oriented facing forward in the consist. Setting CV to a value between 129 and 255 enables consist addresses 1 to 127 with the locomotive oriented facing backwards in the consist.

### Default Value:

0

## Related CVs:

See also Primary Address, Consist Function Active, Consist F0 Function Active.

## CV 21 Consist Function Group 1

### Description

Defines which Group 1 functions may be controlled by packets sent to the decoder's consist address. Disabled functions may be controlled only from decoder's primary or extended address:

| Bit 7  |    |    |    |             |            |                           | Bit 0 |

|--------|----|----|----|-------------|------------|---------------------------|-------|

| F7     | F6 | F5 | F4 | F3          | F2         | F1                        | F0    |

| Bit 0: |    | (  |    | on is disab | led for co | nsist oper<br>nsist opera |       |

| Bit 1: |    | (  |    | on is disab | led for co | nsist oper<br>nsist oper  |       |

| Bit 2: |    | (  |    | on is disab | led for co | nsist oper<br>nsist opera |       |

| Bit 3: |    | (  |    | on is disab | led for co | nsist oper<br>nsist opera |       |

| Bit 4: |    | (  |    | on is disab | led for co | nsist oper<br>nsist oper  |       |

| Bit 5: |    | (  |    | on is disab | led for co | nsist oper<br>nsist opera |       |

| Bit 6: |    | (  |    | on is disab | led for co | nsist oper<br>nsist opera |       |

| Bit 7: |    | (  |    | on is disab | led for co | nsist oper<br>nsist oper  |       |

This register is useful for differentiating the lead engine in the consist from the other engines.

| Default Value: | 0                                                     |

|----------------|-------------------------------------------------------|

| Related CVs:   | See also Consist Address, Consist F0 Function Active. |

|                | Consist F0 Function Active.                           |

## CV 22 Consist Function Group 2

### Description

Defines which Group 2 functions may be controlled by packets sent to the decoder's consist address. Disabled functions may be controlled only from decoder's primary or extended address:

| Bit 7  |         |     |             |             |                           | Bit 0  |

|--------|---------|-----|-------------|-------------|---------------------------|--------|

|        | F12     | F11 | F10         | F9          | F0 (r)                    | F0 (f) |

| Bit 0: | (       |     | on is disab | oled for co | nsist oper<br>nsist oper  |        |

| Bit 1: | (       |     | on is disab | oled for co | nsist oper<br>nsist opera |        |

| Bit 2: | (       |     | on is disab | oled for co | nsist oper<br>nsist oper  |        |

| Bit 3: | (       |     | on is disab | oled for co | nsist oper<br>nsist opera |        |

| Bit 4: | (       |     | on is disat | oled for co | nsist oper<br>nsist oper  |        |

| Bit 5: | (       |     | on is disat | oled for co | nsist oper<br>nsist oper  |        |

| Bit 6: | Reserve | d.  |             |             |                           |        |

| Bit 7: | Reserve | d.  |             |             |                           |        |

This register is useful for differentiating the Headlight and Backup Light functions in the lead engine of the consist from the other engines. For example, by setting this register in the lead locomotive to 1 and the same register in all other engines to 0, only the headlight in the lead engine will be on and only when the consist is moving forward.

| Default Value: | 0                                                  |

|----------------|----------------------------------------------------|

| Related CVs:   | See also Consist Address, Consist Function Active. |

## CV 23 Consist Acceleration Rate

### Description

Contains a value between -127 to +127 corresponding to the decoder's consist acceleration offset:

| Bit 7            |    |                  |                           |            |         |    | Bit 0 |

|------------------|----|------------------|---------------------------|------------|---------|----|-------|

| sign             | D6 | D5               | D4                        | D3         | D2      | D1 | D0    |

| Bits (<br>Bit 7: |    | D0-D6, C<br>Sign | Consist Ac                | celeratior | n value |    |       |

|                  |    | (                | 0 = positiv<br>1 = negati |            |         |    |       |

When the consist address is active, the consist acceleration rate is added to or subtracted from the decoder's base acceleration rate depending on the sign bit. The acceleration is then computed as:

#### seconds/speed step = (CV 3 + CV 23) x 0.896+Number of speed steps

If the sum of CV 3 and CV 23 is negative, then the acceleration rate is set to 0 (i.e., acceleration is instant.) If the sum of CV 3 and CV 23 exceeds 255, then the acceleration rate is set to the maximum value of 255.

This CV has no effect when the consist address is set to 0.

In summary, a CV value between 0 and 127 will increase the decoder's base acceleration rate. Values between 128 and 255 will decrease the decoder's base acceleration rate.

Default value: Related CVs: 0

See also Baseline Acceleration Rate, Baseline Braking Rate, Consist Brake Rate.

## CV 24 Consist Braking Rate

### Description

Contains a value between -127 to +127 corresponding to the decoder's consist braking offset:

| Bit 7 |    |    |    |    |    |    | Bit 0 |

|-------|----|----|----|----|----|----|-------|

| sign  | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

| Bits 0-6: | D0-D6, Consist Braking value             |

|-----------|------------------------------------------|

| Bit 7:    | Sign                                     |

|           | 0 = positive value<br>1 = negative value |

When the consist address is active, the consist braking rate is added to or subtracted from the decoder's baseline braking rate depending on the sign bit. The braking rate is then computed as:

#### seconds/speed step = (CV 4 + CV 24) x 0.896+Number of speed steps

If the sum of CV 4 and CV 24 is negative, then the braking rate is set to 0 (i.e., braking is instant.) If the sum of CV 4 and CV 24 exceeds 255, then the braking rate is set to the maximum value of 255.

This CV has no effect when the consist address is set to 0.

In summary, a CV value between 0 and 127 will increase the decoder's base braking rate. Values between 128 and 255 will decrease the decoder's base braking rate.

Default value: Related CVs: 0

See also Baseline Acceleration Rate, Baseline Braking Rate, Consist Acceleration Rate.

## CV 25 Speed Table Select Register

### Description

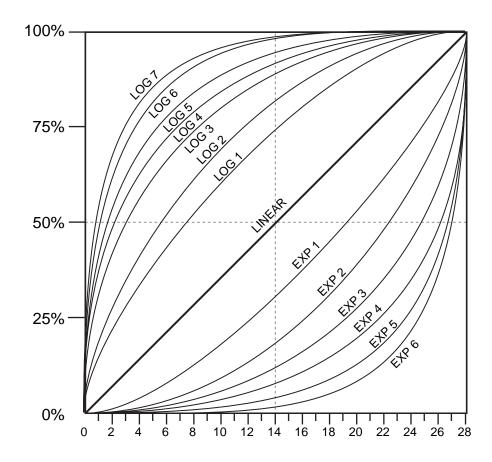

Used to select one of 15 Speed Curves:

| Bit 7  |    |    |    |    |    |    | Bit 0 |

|--------|----|----|----|----|----|----|-------|

| MIDSPD | D6 | D5 | D4 | D3 | D2 | D1 | D0    |

| D0-D6:  | Table Identifier/Speed Step Value |

|---------|-----------------------------------|

| MIDSPD: | 0 = Factory Speed Table Select    |

|         | 1 = Mid Range Speed (Not used)    |

When MIDSPD = 0, D0-D6 defines which preset factory speed table is used.

- 0 = Disabled, Speed Curves not used

- 1 = Disabled, Speed Curves not used

- 2 = Linear Speed Curve

- 3 = Logarithmic Curve 1

- 4 = Logarithmic Curve 2

- 5 = Logarithmic Curve 3

- 6 = Logarithmic Curve 4

- 7 = Logarithmic Curve 5

- 8 = Logarithmic Curve 6

- 9 = Logarithmic Curve 7

- 10 = Exponential Curve 1

- 11 = Exponential Curve 2

- 12 = Exponential Curve 3

- 13 = Exponential Curve 4

- 14 = Exponential Curve 5

- 15 = Exponential Curve 6

- 16 = User Defined Speed Table defined by CVs 67-94.

CV 25 may be programmed with any value between 0 and 31. Values between 2 and 15 allow the user to select from one of 14 predefined speed curves as depicted below. The logarithmic curves provide a shallower speed response as the throttle is increased. These curves are useful for locomotives that require a high starting voltage to get moving or matching a highly geared locomotive to one that has less gearing. The exponential curves are useful for slowing down locomotives that have a "slot car" response.

Setting this CV to a value of 16 will enable the speed curve programmed into CVs 67-94. This curve may be programmed by the user to get virtually any response desired.

Note that in order for the selected curve to be active, bit 4 of CV 29 must also be set to 1. If CV 29, bit 4 is 0, the throttle response will be linear (straight line).

The speed curves can be used in 14, 28 and 128 speed step modes.

Bit 7 is defined by the NMRA RPs as the Mid Range Speed Step select bit. The Decoder does not implement this feature and will ignore commands that attempt to program this bit with a 1 (i.e., data values between 128-255).

Default value:0Related CVs:See also CV 29, Loadable Speed Table.

## CV 29 Configuration Register 1

### Description

CV 29 contains miscellaneous decoder configuration bits:

| Bit 7  |   | Joenancoa                | 0 00000                                               | roomigan                            |                     |                                  | Bit 0      |  |  |

|--------|---|--------------------------|-------------------------------------------------------|-------------------------------------|---------------------|----------------------------------|------------|--|--|

| 0      | 0 | EAM STE ACK Res. F0 [    |                                                       |                                     |                     |                                  |            |  |  |

| Bit 0: |   | 0 = norm<br>1 = direc    | ection Bit<br>nal operati<br>tion bit in<br>rocessing | Speed/Di                            | rection in:         | struction is                     | s inverted |  |  |

| Bit 1: |   | Instruction<br>1 = F0 st | tate is cor<br>on (14 Spo<br>tate is cor              | eed Step                            | Mode)<br>bit 4 of F | peed/Dire<br>unction G<br>lodes) |            |  |  |

| Bit 2: |   | Reserve                  | d.                                                    |                                     |                     |                                  |            |  |  |

| Bit 3: |   | 0 = Adva                 | anced Acl                                             | knowledge<br>knowledge<br>knowledge | e mode di           |                                  | ot used)   |  |  |

| Bit 4: |   | 0 = Spee                 |                                                       | et by CV                            |                     | by CV 25                         |            |  |  |

| Bit 5: |   | 0 = Decc                 | oder respo                                            |                                     | imary Ado           | e<br>Iress in C'<br>ddress in (  |            |  |  |

| Bit 6: |   | Reserve                  | d.                                                    |                                     |                     |                                  |            |  |  |

| Bit 7: |   | Multifund                | ction Deco                                            | oder - Alw                          | ays reads           | as 0.                            |            |  |  |

When the DIR bit is set, the locomotive and headlight will run in a direction opposite to the speed/direction instruction received. This bit is mostly useful for diesel locomotives that are run long hood forward and has little use for steam operation.

The F0 bit should be cleared to 0 if you are using the decoder in 14 speed step mode. If you are using 28 or 128 speed step modes, this bit should be set to 1.

The STE bit must be set to 1 in order to enable any of the speed curves selected using CV 25. Otherwise, the decoder will provide a linear (straight-line) throttle response.

The EAM bit must be set to 1 in order to activate extended address capability. Note that once this bit is set, the decoder will respond to commands sent to the extended address only and commands sent to the primary address will be ignored. This can be a problem if you are using a command station that does not support extended addressing and the bit gets accidentally set. In such a case, you must connect the decoder to a programming track to gain access to the CV and clear the bit.

The APS bit must be set to 1 in order to activate an alternate power mode as set in CV 12. To activate Analog Mode Operation, you must also set CV 12 to 1. Note: this feature is not contained in all versions.

The decoder does not support advanced acknowledgment and the ACK bit will always read as 0.

Default value: Related CVs:

## CV 30 Error Information/Alternate Mode Selection

### Description

Contains manufacturer defined error codes and provides feedback in the event an operational failure occurred within the decoder. It is also used to re-configure the decoder for non-NMRA compliant options:

| Bit 7            |                                                                                                                                                                                                                                             |                                                                                                                    |  |             |           | Bit 0    |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|-------------|-----------|----------|--|--|--|

|                  |                                                                                                                                                                                                                                             |                                                                                                                    |  | GRP23       | CVCLR     | CVLCKE   |  |  |  |

| Bit 0:<br>Bit 1: | 0 = Norma<br>1 = Enable<br>CVCLR, C                                                                                                                                                                                                         | CVLCKE, CV Lock Enable<br>0 = Normal operation.<br>1 = Enables CV Lock as set in CVs 15 and 16.<br>CVCLR, CV Clear |  |             |           |          |  |  |  |

|                  | 0 = Norma<br>1 = All CV<br>cycle.                                                                                                                                                                                                           | •                                                                                                                  |  | lefault val | ues at ne | xt power |  |  |  |

| Bit 2:           | GRP23, Function Group 2 and 3 Exchange<br>0 = System Normal, Decoder processes group 2 and 3<br>function commands according to the NMRA standard.<br>1 = Function Group 2 (F5-F8) assignments are swapped<br>with Function Group 3 (F9-F12) |                                                                                                                    |  |             |           |          |  |  |  |

| Bits 3-7:        | Reserved.                                                                                                                                                                                                                                   |                                                                                                                    |  |             |           |          |  |  |  |

Default value:0Related CVs:See also CV Unlock Register, CV Lock ID Code.

## CV 33-46 Function Output Map

CVs 33-46 allow the user to customize which decoder outputs are controlled by which function keys. Each function input, F0 through F12, is assigned a unique CV that allows the corresponding function control to be redirected to up to fifteen different decoder function outputs. This allows a single function key to control more than one output if desired.

The F0 function has two CVs - one for forward direction and one for reverse. Function outputs mapped to these registers will be directional unless the same output is mapped to both CVs.

Note that all function inputs cannot be mapped to all outputs. The matrix below graphically indicates which inputs can control which outputs:

| Function Mapping Table |            |           |              |            |          |          |          |          |          |          |          |        |          |          |        |          |

|------------------------|------------|-----------|--------------|------------|----------|----------|----------|----------|----------|----------|----------|--------|----------|----------|--------|----------|

| Function Key           | Control CV | Headlight | Backup Light | Xing Logic | RESERVED | Dimmer | RESERVED | RESERVED | Brakes | RESERVED |

| F0 (f)                 | 33         | 1         | 2            | 4          | 8        | 16       | 32       | 64       | 128      |          |          |        |          |          |        |          |

| F0 (r)                 | 34         | 1         | 2            | 4          | 8        | 16       | 32       | 64       | 128      |          |          |        |          |          |        |          |

| F1                     | 35         | 1         | 2            | 4          | 8        | 16       | 32       | 64       | 128      |          |          |        |          |          |        |          |

| F2                     | 36         | 1         | 2            | 4          | 8        | 16       | 32       | 64       | 128      |          |          |        |          |          |        |          |

| F3                     | 37         |           |              |            | 1        | 2        | 4        | 8        | 16       | 32       | 64       | 128    |          |          |        |          |

| F4                     | 38         |           |              |            | 1        | 2        | 4        | 8        | 16       | 32       | 64       | 128    |          |          |        |          |

| F5                     | 39         |           |              |            | 1        | 2        | 4        | 8        | 16       | 32       | 64       | 128    |          |          |        |          |

| F6                     | 40         |           |              |            | 1        | 2        | 4        | 8        | 16       | 32       | 64       | 128    |          |          |        |          |

| F7                     | 41         |           |              |            |          |          |          | 1        | 2        | 4        | 8        | 16     | 32       | 64       | 128    |          |

| F8                     | 42         |           |              |            |          |          |          | 1        | 2        | 4        | 8        | 16     | 32       | 64       | 128    |          |

| F9                     | 43         |           |              |            |          |          |          | 1        | 2        | 4        | 8        | 16     | 32       | 64       | 128    |          |

| F10                    | 44         |           |              |            |          |          |          |          | 1        | 2        | 4        | 8      | 16       | 32       | 64     | 128      |

| F11                    | 45         |           |              |            |          |          |          |          | 1        | 2        | 4        | 8      | 16       | 32       | 64     | 128      |

| F12                    | 46         |           |              |            |          |          |          |          | 1        | 2        | 4        | 8      | 16       | 32       | 64     | 128      |

Bold Numbers indicate default settings.

## CV 33 F0(f) Output Location

### **Description**

Maps the FO(fwd) function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7  |      |          |                                                                                                                                            |      |  |  | Bit 0 |  |  |  |

|--------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|-------|--|--|--|

| Res.   | Res. | Res.     | Res. Res. Res. Xing BL                                                                                                                     |      |  |  |       |  |  |  |

| Bit 0: |      | 0 = Outp | HL, Head light output<br>D = Output is unaffected by F0(fwd).<br>1 = Output is activated when F0(fwd) is on.                               |      |  |  |       |  |  |  |

| Bit 1: |      | 0 = Outp | <ul><li>BL, Backup light output</li><li>0 = Output is unaffected by F0(fwd).</li><li>1 = Output is activated when F0(fwd) is on.</li></ul> |      |  |  |       |  |  |  |

| Bit 2: |      | Grade C  | rossing Lo                                                                                                                                 | ogic |  |  |       |  |  |  |

| Bit 3: |      | Reserve  | d.                                                                                                                                         |      |  |  |       |  |  |  |

| Bit 4: |      | Reserve  | d.                                                                                                                                         |      |  |  |       |  |  |  |

| Bit 5: |      | Reserve  | Reserved.                                                                                                                                  |      |  |  |       |  |  |  |

| Bit 6: |      | Reserve  | Reserved.                                                                                                                                  |      |  |  |       |  |  |  |

| Bit 7: |      | Reserve  | d.                                                                                                                                         |      |  |  |       |  |  |  |

## CV 34 F0(r) Output Location

### Description

Maps the F0(rev) function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Res. | Res. | Res. | Res. | Res. | Xing | BL | HL |  |

|------|------|------|------|------|------|----|----|--|

| Bit 0: | HL, Head light output<br>0 = Output is unaffected by F0(rev).<br>1 = Output is activated when F0(rev) is on.                               |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 1: | <ul><li>BL, Backup light output</li><li>0 = Output is unaffected by F0(rev).</li><li>1 = Output is activated when F0(rev) is on.</li></ul> |

| Bit 2: | Grade Crossing Logic.                                                                                                                      |

| Bit 3: | Reserved.                                                                                                                                  |

| Bit 4: | Reserved.                                                                                                                                  |

| Bit 5: | Reserved.                                                                                                                                  |

| Bit 6: | Reserved.                                                                                                                                  |

| Bit 7: | Reserved.                                                                                                                                  |

Bit 0

## CV 35 F1 Output Location

### Description

Maps the F1 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

#### Bit 7

| Res. | Res. | Res. | Res.   | Res.  | Xing  | BL | HL |

|------|------|------|--------|-------|-------|----|----|

| noor |      | Roor | i tooi | 11001 | Xiiig | 52 |    |

| Bit 0: | HL, Head light output<br>0 = Output is unaffected by F1.<br>1 = Output is activated when F1 is on.   |

|--------|------------------------------------------------------------------------------------------------------|

| Bit 1: | BL, Backup light output<br>0 = Output is unaffected by F1.<br>1 = Output is activated when F1 is on. |

| Bit 2: | Grade Crossing Logic                                                                                 |

| Bit 3: | Reserved.                                                                                            |

| Bit 4: | Reserved.                                                                                            |

| Bit 5: | Reserved.                                                                                            |

| Bit 6: | Reserved.                                                                                            |

| Bit 7: | Reserved.                                                                                            |

Bit 0

## CV 36 F2 Output Location

### Description

Maps the F2 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7 |      |                                                                                                      |                                                                                                    |      |  |  | Bit 0 |  |  |  |  |

|-------|------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|--|--|-------|--|--|--|--|

| Res.  | Res. | Res.                                                                                                 | Res. Res. Res. Xing BL                                                                             |      |  |  |       |  |  |  |  |

| Bit 0 | :    | 0 = Outp                                                                                             | HL, Head light output<br>0 = Output is unaffected by F2.<br>1 = Output is activated when F2 is on. |      |  |  |       |  |  |  |  |

| Bit 1 |      | BL, Backup light output<br>0 = Output is unaffected by F2.<br>1 = Output is activated when F2 is on. |                                                                                                    |      |  |  |       |  |  |  |  |

| Bit 2 |      | Grade C                                                                                              | rossing Lo                                                                                         | ogic |  |  |       |  |  |  |  |

| Bit 3 |      | Reserve                                                                                              | d.                                                                                                 |      |  |  |       |  |  |  |  |

| Bit 4 |      | Reserve                                                                                              | d.                                                                                                 |      |  |  |       |  |  |  |  |

| Bit 5 | :    | Reserved.                                                                                            |                                                                                                    |      |  |  |       |  |  |  |  |

| Bit 6 | :    | Reserve                                                                                              | Reserved.                                                                                          |      |  |  |       |  |  |  |  |

| Bit 7 |      | Reserve                                                                                              | d.                                                                                                 |      |  |  |       |  |  |  |  |

## CV 37 F3 Output Location

### Description

Maps the F3 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7  |      |                        |                               |                                                    |             |                    | Bit 0    |  |  |  |  |

|--------|------|------------------------|-------------------------------|----------------------------------------------------|-------------|--------------------|----------|--|--|--|--|

| DIM    | Res. | Res.                   | Res. Res. Res. Res. Res. Res. |                                                    |             |                    |          |  |  |  |  |

| Bit 0: |      | Reserve                | Reserved.                     |                                                    |             |                    |          |  |  |  |  |

| Bit 1: |      | Reserve                | d.                            |                                                    |             |                    |          |  |  |  |  |

| Bit 2: |      | Reserved.              |                               |                                                    |             |                    |          |  |  |  |  |

| Bit 3: |      | Reserved.              |                               |                                                    |             |                    |          |  |  |  |  |

| Bit 4: |      | Reserve                | d.                            |                                                    |             |                    |          |  |  |  |  |

| Bit 5: |      | Reserve                | d                             |                                                    |             |                    |          |  |  |  |  |

| Bit 6: |      | Reserved.              |                               |                                                    |             |                    |          |  |  |  |  |

| Bit 7: |      | 0 = Light<br>1 = Light | ing outpu                     | mmer Fur<br>ts are una<br>ts set up a<br>F3 is on. | affected by | y F3.<br>able Heac | llights" |  |  |  |  |

Default Value:0Related CVs:See also CVs 33-36, 38-46

## CV 38 F4 Output Location

### **Description**

Maps the F4 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7 Bit |      |                                                                                                                                                                                                |                               |  |  |  |  |  |  |

|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| DIM       | Res. | Res.                                                                                                                                                                                           | Res. Res. Res. Res. Res. Res. |  |  |  |  |  |  |

| Bit 0     | ):   | Reserve                                                                                                                                                                                        | d.                            |  |  |  |  |  |  |

| Bit 1:    |      | Reserve                                                                                                                                                                                        | d.                            |  |  |  |  |  |  |

| Bit 2:    |      | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |

| Bit 3:    |      | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |

| Bit 4:    |      | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |

| Bit 5:    |      | Reserved                                                                                                                                                                                       |                               |  |  |  |  |  |  |

| Bit 6:    |      | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |

| Bit 7:    |      | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F4.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F4 is on.</li> </ul> |                               |  |  |  |  |  |  |

Default Value: 0 Related CVs: See also CVs 33-37, 39-46

## CV 39 F5 Output Location

### Description

Maps the F5 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7 Bit 0                                                                                                                                                                  |                  |           |      |      |      |          |      |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|------|------|------|----------|------|--|--|

| DIM                                                                                                                                                                          | Res.             | Res.      | Res. | Res. | Res. | Res.     | Res. |  |  |

| Bit 0                                                                                                                                                                        | :                | Reserve   | d.   |      |      |          |      |  |  |

| Bit 1:                                                                                                                                                                       | :                | Reserve   | d.   |      |      |          |      |  |  |

| Bit 2: Reserved.                                                                                                                                                             |                  |           |      |      |      |          |      |  |  |

| Bit 3: Reserved.                                                                                                                                                             |                  |           |      |      |      |          |      |  |  |

| Bit 4:                                                                                                                                                                       | Bit 4: Reserved. |           |      |      |      |          |      |  |  |

| Bit 5                                                                                                                                                                        | :                | Reserved  |      |      |      |          |      |  |  |

| Bit 6:                                                                                                                                                                       |                  | Reserved. |      |      |      |          |      |  |  |

| <b>Bit 7:</b> DIM, Headlight Dimmer Function<br>0 = Lighting outputs are unaffected by F5.<br>1 = Lighting outputs set up as "Dimmable Headligh<br>are dimmed when F5 is on. |                  |           |      |      |      | llights" |      |  |  |

Default Value:0Related CVs:See also CVs 33-38, 40-46

## CV 40 F6 Output Location

### Description

Maps the F6 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7 Bit |      |                                                                                                                                                                                                |                               |  |  |  |  |  |  |  |

|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|

| DIM       | Res. | Res.                                                                                                                                                                                           | Res. Res. Res. Res. Res. Res. |  |  |  |  |  |  |  |

| Bit 0     | :    | Reserve                                                                                                                                                                                        | d.                            |  |  |  |  |  |  |  |

| Bit 1:    |      | Reserve                                                                                                                                                                                        | Reserved.                     |  |  |  |  |  |  |  |

| Bit 2:    |      | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |  |

| Bit 3     | :    | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |  |

| Bit 4     | :    | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |  |

| Bit 5:    |      | Reserved                                                                                                                                                                                       |                               |  |  |  |  |  |  |  |

| Bit 6:    |      | Reserved.                                                                                                                                                                                      |                               |  |  |  |  |  |  |  |

| Bit 7     | :    | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F6.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F6 is on.</li> </ul> |                               |  |  |  |  |  |  |  |

Default Value:0Related CVs:See also CVs 33-39, 41-46

## CV 41 F7 Output Location

### Description

Maps the F7 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7  |      |                                                                                                                                                                                                |           |                                      |      | _    | Bit 0 |  |  |  |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------|------|------|-------|--|--|--|

| BRK    | Res. | Res.                                                                                                                                                                                           | DIM       | Res.                                 | Res. | Res. | Res.  |  |  |  |

| Bit 0: |      | Reserve                                                                                                                                                                                        | Reserved. |                                      |      |      |       |  |  |  |

| Bit 1: |      | Reserve                                                                                                                                                                                        | Reserved. |                                      |      |      |       |  |  |  |

| Bit 2: |      | Reserved                                                                                                                                                                                       | b         |                                      |      |      |       |  |  |  |

| Bit 3: |      | Reserved.                                                                                                                                                                                      |           |                                      |      |      |       |  |  |  |

| Bit 4: |      | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F7.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F7 is on.</li> </ul> |           |                                      |      |      |       |  |  |  |

| Bit 5: |      | Reserved.                                                                                                                                                                                      |           |                                      |      |      |       |  |  |  |

| Bit 6: |      | Reserved.                                                                                                                                                                                      |           |                                      |      |      |       |  |  |  |

| Bit 7: |      | 0 = Braki                                                                                                                                                                                      | -         | ng Effect<br>ffected by<br>vated whe |      | ٦.   |       |  |  |  |

Default Value:16Related CVs:See also CVs 33-40, 42-46

## CV 42 F8 Output Location

### Description

Maps the F8 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7            |                  |                                                                                                                                                                                                |     |                                      |      |      | Bit 0 |  |  |

|------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------|------|------|-------|--|--|

| BRK              | Res.             | Res.                                                                                                                                                                                           | DIM | Res.                                 | Res. | Res. | Res.  |  |  |

| Bit 0: Reserved. |                  |                                                                                                                                                                                                |     |                                      |      |      |       |  |  |

| Bit 1            | :                | Reserved.                                                                                                                                                                                      |     |                                      |      |      |       |  |  |

| Bit 2:           |                  | Reserve                                                                                                                                                                                        | d.  |                                      |      |      |       |  |  |

| Bit 3            | :                | Reserved.                                                                                                                                                                                      |     |                                      |      |      |       |  |  |

| Bit 4:           |                  | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F8.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F8 is on.</li> </ul> |     |                                      |      |      |       |  |  |

| Bit 5            | :                | Reserved.                                                                                                                                                                                      |     |                                      |      |      |       |  |  |

| Bit 6            | Bit 6: Reserved. |                                                                                                                                                                                                |     |                                      |      |      |       |  |  |

| Bit 7            | :                | 0 = Brak                                                                                                                                                                                       |     | ng Effect<br>ffected by<br>vated whe |      | ٦.   |       |  |  |

Default Value:0Related CVs:See also CVs 33-41, 43-46

## CV 43 F9 Output Location

### Description

Maps the F9 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7            |      |                                                                                                                                                                   |     |                                      |      |      | Bit 0 |  |  |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------|------|------|-------|--|--|

| BRK              | Res. | Res.                                                                                                                                                              | DIM | Res.                                 | Res. | Res. | Res.  |  |  |

| Bit 0            | -    | Reserved.<br>Reserved.                                                                                                                                            |     |                                      |      |      |       |  |  |

| Bit 2            | :    | Reserve                                                                                                                                                           | d   |                                      |      |      |       |  |  |

| Bit 3:           |      | Reserved.                                                                                                                                                         |     |                                      |      |      |       |  |  |

| Bit 4:           |      | DIM, Headlight Dimmer Function<br>0 = Lighting outputs are unaffected by F9.<br>1 = Lighting outputs set up as "Dimmable Headlights"<br>are dimmed when F9 is on. |     |                                      |      |      |       |  |  |

| Bit 5:           |      | Reserved.                                                                                                                                                         |     |                                      |      |      |       |  |  |

| Bit 6: Reserved. |      |                                                                                                                                                                   |     |                                      |      |      |       |  |  |

| Bit 7            | :    | 0 = Brak                                                                                                                                                          | -   | nh Effect<br>ffected by<br>vated whe |      | ٦.   |       |  |  |

Default Value:0Related CVs:See also CVs 33-42, 44-46

### CV 44 F10 Output Location

#### Description

Maps the F10 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7  |     |                                                                                                                                                                                                  |           |     |     |      | Bit 0 |  |  |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|------|-------|--|--|

| Res.   | BRK | Res.                                                                                                                                                                                             | Res.      | DIM | Res | Res. | Res.  |  |  |

| Bit 0: |     | Reserve                                                                                                                                                                                          | Reserved. |     |     |      |       |  |  |

| Bit 1: |     | Reserved                                                                                                                                                                                         |           |     |     |      |       |  |  |

| Bit 2: |     | Reserved.                                                                                                                                                                                        |           |     |     |      |       |  |  |

| Bit 3: |     | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F10.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F10 is on.</li> </ul> |           |     |     |      |       |  |  |

| Bit 4: |     | Reserved                                                                                                                                                                                         | d.        |     |     |      |       |  |  |

| Bit 5: |     | Reserved.                                                                                                                                                                                        |           |     |     |      |       |  |  |

| Bit 6: |     | BRK, Motor Braking Effects<br>0 = Braking is unaffected by F10.<br>1 = Braking is activated when F10 is on.                                                                                      |           |     |     |      |       |  |  |

| Bit 7: |     | Reserved                                                                                                                                                                                         | d.        |     |     |      |       |  |  |

Default Value:0Related CVs:See also CVs 33-43, 45-46

### CV 45 F11 Output Location

#### Description

Maps the F11 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7  |     |                                                                                                                                                                                                  |           |     |     | _    | Bit 0 |  |  |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----|------|-------|--|--|

| Res.   | BRK | Res.                                                                                                                                                                                             | Res.      | DIM | Res | Res. | Res.  |  |  |

| Bit 0: |     | Reserve                                                                                                                                                                                          | Reserved. |     |     |      |       |  |  |

| Bit 1: |     | Reserved                                                                                                                                                                                         |           |     |     |      |       |  |  |

| Bit 2: |     | Reserved.                                                                                                                                                                                        |           |     |     |      |       |  |  |

| Bit 3: |     | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F11.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F11 is on.</li> </ul> |           |     |     |      |       |  |  |

| Bit 4: |     | Reserved                                                                                                                                                                                         | d.        |     |     |      |       |  |  |

| Bit 5: |     | Reserved.                                                                                                                                                                                        |           |     |     |      |       |  |  |

| Bit 6: |     | BRK, Motor Braking Effect<br>0 = Braking is unaffected by F11.<br>1 = Braking is activated when F11 is on.                                                                                       |           |     |     |      |       |  |  |

| Bit 7: |     | Reserved                                                                                                                                                                                         | b         |     |     |      |       |  |  |

Default Value:64Related CVs:See also CVs 33-44, 46

### CV 46 F12 Output Location

#### Description

Maps the F12 function to any of eight decoder auxiliary function outputs as defined by a 1 in the corresponding bit position:

| Bit 7  |     |                                                                                                                                                                                                  |      |     |     |      | Bit 0 |  |

|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|-------|--|

| Res.   | BRK | Res.                                                                                                                                                                                             | Res. | DIM | Res | Res. | Res.  |  |

| Bit 0: |     | Reserved.                                                                                                                                                                                        |      |     |     |      |       |  |

| Bit 1: |     | Reserved                                                                                                                                                                                         |      |     |     |      |       |  |

| Bit 2: |     | Reserved.                                                                                                                                                                                        |      |     |     |      |       |  |

| Bit 3: |     | <ul> <li>DIM, Headlight Dimmer Function</li> <li>0 = Lighting outputs are unaffected by F12.</li> <li>1 = Lighting outputs set up as "Dimmable Headlights" are dimmed when F12 is on.</li> </ul> |      |     |     |      |       |  |

| Bit 4: |     | Reserved                                                                                                                                                                                         | d.   |     |     |      |       |  |

| Bit 5: |     | Reserved.                                                                                                                                                                                        |      |     |     |      |       |  |

| Bit 6: |     | BRK, Motor Braking Effect<br>0 = Braking is unaffected by F12.<br>1 = Braking is activated when F12 is on.                                                                                       |      |     |     |      |       |  |

| Bit 7: |     | Reserved                                                                                                                                                                                         | d.   |     |     |      |       |  |

Default Value:0Related CVs:See also CVs 33-45

# Lighting Effect CVs

### CV 49-50 Hyperlight Effect Select

#### Description

Used to set the Hyperlight lighting effect and control mode for their respective output:

CV 49, Headlight Effect Select

CV 50, Backup Light Effect Select

| Bit 7 |      |                                                                                    |                                                                                           |                                                                                                                                           |                                                      |            | Bit 0 |

|-------|------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------|-------|

| LED   | R17  | XING                                                                               | PHSE                                                                                      | EF3                                                                                                                                       | EF2                                                  | EF1        | EF0   |

| Bits  | 0-3: | 0 =<br>1 =<br>2 =<br>3 =<br>4 =<br>5 =<br>6 =<br>7 =<br>8 =<br>9 =<br>10 =<br>11 = | Rule Mars<br>Mars<br>Pyle C<br>Single<br>Doubl<br>Weste<br>Prime<br>Type<br>FRED<br>Engin | f output<br>17 Dimma<br>Light<br>Gyralite<br>ating Head<br>Flash Str<br>Flash St<br>ern Cullen<br>Stratolite<br>Ditch Lig<br>II Ditch Lig | robe<br>trobe<br>D312 Ro<br>ht<br>ght<br>Frain flash | tary Beaco | on    |

Most of the effects are self-descriptive. However a few need some additional notes:

**Dimmable Headlight** - The function output is normally an on/off output. If the output is on, the output level will be reduced about 60% whenever the dimmer function is on.

**Type I and Type II Ditch Lights** - These are identical when operating. However, if the grade crossing logic is enabled, the Type I ditch light will revert to a steady on state when it is not flashing whereas the Type II lights will turn off.

**Engine Exhaust** - This effect produces a random flicker whose intensity is proportional to the engine RPMs. It is best used by placing a red/ orange lamp under the model's exhaust port, out of direct view. As the engine is revved up, it will glow brighter, imitating unmuffled exhaust gases and sparks.

**Dyno-Light** - This effect for diesel locomotives softly fades the lamp brightness on and off to simulate the heating and cooling of the bulb filament.

Bit 4: PHSE, Phase Select Bit 0 = Phase A 1 = Phase B

**Phase Select Bit** - Alters the timing of the effect so that it is 180 degrees out of phase with the other effects. This allows you to have two light effects that blink back and forth if desired. Set one effect to phase A and the other to phase B.

Bit 5:XING, Grade Crossing Logic Enable0 = Crossing Logic disabled1 = Crossing Logic enabled when Horn function is on.

*Grade Crossing Logic Bit* - Causes the lighting effect to become active only when function two has been activated (and the corresponding lighting function key is also on). A typical use would be to cause the ditch lights to flash at a grade crossing. The grade crossing logic can be used with almost all the Hyperlight effects. The on/off, dimmable headlight, FRED, engine exhaust, and firebox flicker effects will not be affected. The other effects will either turn off (strobes and beacons) or revert to a steady on state (mars light, ditch lights, etc.) as appropriate to prototype practice.

Bit 6: R17, Rule 17 Mode 0 = Rule 17 Mode disabled 1 = Rule 17 Mode enabled

**Rule 17 Mode** - Converts the headlight and backup light to independent, non-directional lights. When this mode is active, the headlight is controlled as if it were FX5 and the backup light as FX6 and vice-versa.

Bit 7:

LED, LED Compensation Enable

0 = Incandescent Compatible Lighting Outputs enabled

1 = LED Compatible Lighting Outputs enabled

*LED Compensation* - Improves lighting effect contrast when using LEDs instead of incandescent lamps.

Default Value: